# CONTROL OF SWITCHED DYNAMICAL SYSTEM

A synopsis submitted to Gujarat Technological University for partial fulfilment of the requirement

for the degree of

# **Doctor of Philosophy**

in

# **Instrumentation and Control Engineering**

by

# Hardik R. Patel (Enrollment No. 189999917009)

under the supervision of

Dr. Ankit K. Shah

# GUJARAT TECHNOLOGICAL UNIVERSITY AHMEDABAD, GUJARAT, INDIA

[July-2023]

# **CONTENT**

- 1. Title of the thesis and Abstract

- 2. A brief description on the state of the art of the research topic

- 3. Definition of the Problem

- 4. Objective of work

- 5. Original Contribution by the thesis

- 6. Methodology of Research, Results / Comparisons

- 7. Achievements with respect to objectives

- 8. Conclusion

- 9. List of Publications

- 10. References

#### 1. Title of the Thesis and Abstract

#### Title:

Control of Switched Dynamical System

#### Abstract:

This thesis delves into the domain of control theory, with a particular emphasis on Switched Dynamical Systems (SDS) due to their extensive applicability across various disciplines. SDS comprise multiple subsystems or modes, each exhibiting distinct dynamic behaviours, governed by a switching mechanism orchestrating transitions between these modes. The inherent complexity and mode-switching dynamics of such systems necessitate specialized control strategies to ensure stability, performance, and robustness. The primary objective of this research is to investigate the control of SDS and explore effective techniques and algorithms for stabilizing and regulating these systems, focusing on power electronics converters like boost and buck converters, where a boundary-based control scheme is employed. This scheme is tailored to regulate the output voltage, mitigate disturbances, and achieve desirable transient and steady-state performance, facilitating seamless transitions between different control modes.

The work presents a comparative analysis to evaluate the effectiveness of the suggested control scheme in boost and buck converters, assessing multiple performance metrics, including steady-state accuracy, transient response, robustness against disturbances, and control effort. Through a comprehensive comparison with state-of-the-art techniques, this study provides valuable insights into the strengths and weaknesses of the proposed scheme, contributing to a deeper understanding of its potential and applicability in practical converter systems.

Moreover, the study focuses on the viability of the proposed control scheme through a comprehensive stability analysis, recognizing the pivotal role of stability in sustaining desired performance under varying operating conditions. The control design heavily relies on stability principles, and the analysis further investigates the control scheme's robustness to provide valuable insights into its overall effectiveness.

To validate the proposed control scheme's effectiveness, a hardware implementation is conducted using the FPGA-in-the-Loop (FIL) technique, enabling rapid prototyping and real-

time experimentation on an efficient and flexible platform. By implementing the control algorithm on an FPGA, experimental validations are performed, offering practical insights into the performance and feasibility of the proposed control scheme in real-world applications.

In conclusion, this research aims to advance the field of control theory by investigating effective control strategies for SDS, with a primary focus on boost and buck converters. The study encompasses theoretical analysis, comparative assessments, and hardware implementation, contributing to an enhanced understanding and application of control techniques in complex systems with mode-switching dynamics.

# 2. Brief description on the state of the art of the research topic

The field of "Control of Switched Dynamical Systems" had seen significant advancements, and researchers were actively exploring various aspects of this topic. This research area deals with the control and analysis of dynamical systems that can switch between different modes of behaviour or operation. These systems find wide applications across various domains, including engineering (e.g., power electronics, robotics, and transportation systems), computer science (e.g., network protocols and cyber-physical systems), economics (e.g., financial markets and economic models), and many other disciplines where a system's behaviour can dynamically switch due to external stimuli, internal dynamics, or other influencing factors [1].

The research on control techniques for DC-DC converters, specifically focusing on SDS and hybrid systems, has seen significant progress and innovation. Both Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM) converters require controllers that respond quickly and accurately to load and input voltage changes. One commonly used approach is the Proportional-Integral-Derivative (PID) controller, which adjusts the converter's duty cycle based on the output error [2]. While PID controllers are easy to implement, tuning them can be time-consuming and require trial-and-error experimentation.

To improve control performance, Fractional Order PID (FOPID) controllers have been proposed as superior alternatives to conventional PID controllers [3, 4]. However, achieving the desired closed-loop bandwidth in feedback control is challenging due to the nonminimum phase (NMP) property of DC-DC boost converters [5]. Active disturbance rejection control (ADRC) techniques, which use extended state observers to estimate and cancel out system disturbances, have been studied to address this issue [6]. Nonetheless, variations in system parameters can impact ADRC's effectiveness.

Boundary Control (BC), a geometric-based approach, has been used for regulating DC-DC converter performance [7, 8]. While digital control is gaining popularity, high sampling

rates and processor speeds are necessary for instantaneous voltage and current measurements, limiting practical implementation in high-frequency converters [9]. Robustness and the consideration of non-ideal factors like parametric variations and parasitic parameters are crucial in BC application. Mathematical calculations are necessary for these control approaches [10].

Research has also explored explicit model predictive controllers [11], integration of hybrid automata into cyber-physical systems, and switched linear system models for DC-DC converter control [12]. However, these methods often involve complex and computationally intensive controller designs and may not fully account for physical circuit features and parasitic parameters, leading to potential inaccuracies and uncontrollability.

## 3. Definition of the Problem

The problem of Control of Switched Dynamical Systems involves developing effective control strategies for a class of dynamic systems that undergo switching between different modes or subsystems. These systems can exhibit complex and nonlinear behaviours, making their control challenging. The main objective is to design control algorithms that can regulate the system's behaviour and ensure stability, convergence, or desired performance criteria during transitions between different modes.

The control of switched dynamical systems typically addresses issues such as:

- 1. Mode transitions: How to smoothly and efficiently switch between different subsystems while maintaining stability and achieving desired performance.

- 2. Stability analysis: Ensuring the overall stability of the system during the switching process and in steady-state conditions.

- 3. Convergence: Determining conditions under which the system converges to a desired state or limit cycle, avoiding undesirable oscillations or divergence.

- 4. Control synthesis: Developing control strategies or algorithms that regulate the system's behaviour, tracking desired trajectories, or achieving specific control objectives.

- 5. Robustness: Dealing with uncertainties, disturbances, and modelling errors to ensure the control system's robust performance.

The problem of controlling switched dynamical systems has applications in various fields, including robotics, power systems, manufacturing, and autonomous vehicles, where systems often experience mode changes due to different operational conditions or control inputs.

# 4. Objective and Scope of work

The objective is to develop a comprehensive control framework for effectively regulating the behaviour of SDS. The project aims to design controllers that can manage the system's transitions between different modes or subsystems, ensure stability during mode changes, achieve desired performance objectives, and handle uncertainties. The ultimate goal is to create robust and efficient control strategies for SDS.

# • Modelling of the SDS:

- Develop mathematical models for the SDS that accurately represent its behaviour and dynamics during different modes.

- Account for nonlinearities, uncertainties, and mode-dependent parameters in the system's model to capture real-world complexities.

- Analyse the validity and accuracy of the proposed models through simulation.

# Controller Design:

• Design controllers that can handle mode switching and ensure smooth transitions between different subsystems.

# • Stability Analysis:

- Conduct stability analysis of the proposed control schemes to ensure that the system remains stable during mode changes and steady-state operation.

- Utilize tools like Lyapunov stability analysis to verify the stability of the control system.

## Implementation:

- Implement the designed control algorithms in simulation environments (e.g., MATLAB/Simulink) to validate their effectiveness and performance.

- Evaluate the control system's performance under various scenarios, including normal operation, disturbances, and mode transitions.

- Implement FIL technique on an Artix-7 board, enabling real-time evaluation and testing of its performance and efficacy.

# 5. Original Contribution by the thesis

The following are the key contributions of the research work:

A more realistic representation of the dynamics of boost and buck converters as SDS is achieved by developing a mathematical model that incorporates mode-dependent parameters.

- An advanced control algorithm is introduced for boost and buck converter, specifically

designed to manage mode transitions and ensure stability, convergence, and desired

performance during switching operations.

- The stability properties of the boost and buck converter as SDS are rigorously analysed using Lyapunov methods, providing a profound understanding of the system's stability behaviour.

- The developed control algorithm is successfully implemented on an Artix-7 FPGA board through the FIL technique, enabling real-time evaluation of the control system's performance in hardware.

- A comprehensive comparison is conducted between the proposed control algorithm and conventional methods like PID and FOPID, highlighting the superior performance of the proposed approach.

- Potential challenges and future directions for refining and applying the proposed control strategy in practical systems are discussed, paving the way for future research in this domain.

# 6. Methodology of Research, Results / Comparisons

This research work proposes a methodology for control of SDS. The study explores the effectiveness of a boundary-based control scheme applied to boost and buck converters. To accurately represent the converter circuits with their continuous and discrete states, a hybrid automaton is employed. Different stages of methodologies are discussed for boost converter and buck converter are as follows.

## **6.1** Boost Converter

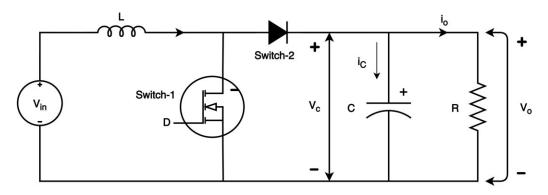

Figure 1 exhibits a traditional configuration of the boost converter, while Table-1 presents the analytical notation employed. It is presumed that all constituents are idealized for the purpose of analysis.

Fig. 1 Typical switched boost converter circuit

Table 1 Notation for analysis of boost converter circuit

| Symbol    | Description                       | $\Delta i_L$ Ripple in inductor current         |                                  |

|-----------|-----------------------------------|-------------------------------------------------|----------------------------------|

| Switch-1  | MOSFET                            | $I_{pkl}$ Peak value of $i_L$ for CCM operation |                                  |

| Switch-2  | Diode                             | $I_{pk2}$ peak value of $i_L$ for DCM operation |                                  |

| f         | Switching frequency of MOSFET     | $V_C$                                           | Average voltage across capacitor |

| D         | Duty cycle                        | $v_o$                                           | Instantaneous output voltage     |

| $V_{in}$  | Input voltage                     | $V_o$                                           | Average output voltage           |

| $V_{ref}$ | Reference or Set-point voltage    | $\Delta v_o$                                    | Output voltage swing             |

| $i_L$     | Instantaneous inductor current    | $M_p$                                           | Peak overshoot                   |

| $I_L$     | Average value of inductor current | $T_s$                                           | Settling time                    |

# **6.1.1** Modelling of boost converter

Let  $X \in \mathbb{R}^n$  be continuous state and k takes values in finite set  $K \triangleq \{1, ..., N\}$  and is discrete state.  $k \in K$  represents the on/off configuration of MOSFET and diode. For each  $k \in K$ , continuous dynamics is modeled by the differential equation as below:

$$\dot{x}(t) = A_{\nu}x(t) + B_{\nu} \tag{1}$$

Where  $x \in X$  is state vector,  $A_k \in R^{n \times n}$  is system matrix and  $B_k \in R^{n \times 1}$ .

The switched system is a special class of hybrid system [13] and mathematically switched dynamical systems can be described by [14],

$$\dot{x}(t) = \int_{-\pi} \left( x(t) \right) \tag{2}$$

Where  $\sigma$  is taking values from index set  $M \stackrel{\text{def}}{=} \{1, ..., m\}$  and m represents the number subsystems.

A hybrid automaton [15] can be defined by tuple  $H = \{K, X, F, I, E, g, TG\}$  which has following components,

- $K = \{k_1, k_2, k_3\}$  is finite set of topologies.

- A state is defined by  $F:(K\times X)\to R^n$ .

- $I:K \to 2^X$  is a mapping that assigns an invariant set  $I_k \subseteq X$  for each topology  $k \in K$ .

- $E \subseteq (K \times K)$  is a set of feasible discrete transitions (or events) allowed among the topologies, such that an element  $e_{ij} = (k_i, k_j) \in E$  implies that a discrete transition from  $i^{th}$  topology to  $j^{th}$  topology is allowed.

- $g:E \to TG$  is guard function such that  $e_{ij} \in E$  to corresponding to guard  $g(e_{ij}) \in TG$ .

- $TG: E \rightarrow 2^X$  is transition guard such that for each  $e_{ij} \in E$ ;  $\exists g(e_{ij}) \in TG$ .

Table 2 Possible discrete state in switched boost Converter

| Discrete state | Switch-1 | Switch-2 |  |

|----------------|----------|----------|--|

| $k_{1}$        | ON       | OFF      |  |

| $k_2$          | OFF      | ON       |  |

| $k_3$          | OFF      | OFF      |  |

| $k_4$          | ON       | ON       |  |

The presence of two switches in the circuit allows for  $2^n$  discrete states. In the case of the second order switched boost converter, this results in four discrete states, as shown in Table-2. Among these states,  $k_4$  is not practicable. Then,  $K = \{k_1, k_2, k_3\}$  are possible discrete state, whereas  $E = [(k_1, k_2), (k_2, k_1), (k_2, k_3), (k_3, k_1)]$  are likely events. Out of these,  $\{(k_1, k_2), (k_2, k_1)\}$  corresponds to CCM operation and  $\{(k_1, k_2), (k_2, k_3), (k_3, k_1)\}$  corresponds to DCM operation of the switched boost converter.

In Figure 1,  $i_L$  and  $v_o$  are the system state variables. It brings three state equations corresponding to  $K_i$ =(i = 1,2,3) as shown in Table-3.

| Operating Mode (k <sub>i</sub> ) | $A_i$                                                                           | $B_i$                                                 |

|----------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------|

| $k_I$                            | $\begin{bmatrix} 0 & 0 \\ 0 & -\frac{1}{RC} \end{bmatrix}$                      | $\begin{bmatrix} \frac{V_{in}}{L} \\ 0 \end{bmatrix}$ |

| $k_2$                            | $\begin{bmatrix} 0 & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{RC} \end{bmatrix}$ | $\begin{bmatrix} \frac{V_{in}}{L} \\ 0 \end{bmatrix}$ |

| $k_3$                            | $\begin{bmatrix} 0 & 0 \\ 0 & -\frac{1}{RC} \end{bmatrix}$                      | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$                |

Table 3 System state matrices corresponding to operating modes of boost converter

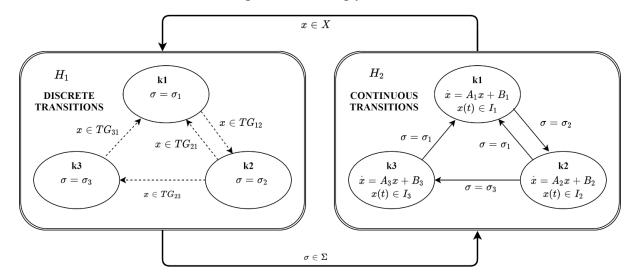

The switched boost converter exhibits both continuous and discrete behaviour because the circuit comprises passive components and switches. So, a hybrid automaton can represent it as shown in Figure 2.  $H_1$  and  $H_2$  represents discrete and continuous transitions, respectively. While  $H_1$  depends on the continuous signal x from  $H_2$ ,  $H_2$  accepts the discrete value  $\sigma \in \Sigma$  from  $H_1$  and the continuous state x grows accordingly.

Fig. 2 Hybrid automaton representation of switched boost converter shown as an interaction of continuous and discrete transitions

# 6.1.2 Controller design for boost converter

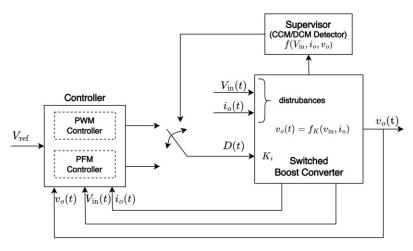

A boundary-based control scheme is presented with simple and nominal mathematical computations. As there are three modes present, three transition guards named TG<sub>12</sub>, TG<sub>23</sub> and TG<sub>31</sub> considered here to control switching between three modes as shown in Figure 2. The selection of proper transition guards makes sure that the state trajectories kept within the limit. The only difference between CCM and DCM operations is, TG<sub>31</sub> is not declared in CCM. The proposed controller architecture is hybrid by using PWM and PFM control schemes for CCM and DCM operations, respectively. Figure 3 shows the resulting closed-loop hybrid control scheme.

Fig. 3 Hybrid control scheme for switched boost converter in the closed-loop

# PWM Controller Design for CCM Operation

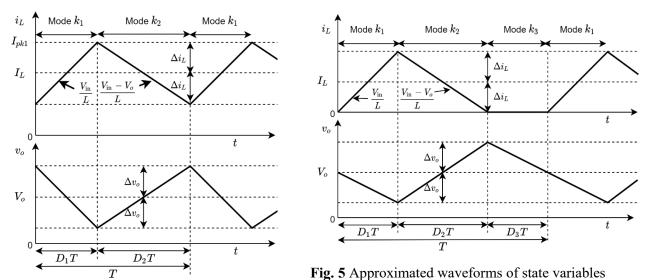

Approximated waveforms of inductor current and output voltage of the switched boost converter operating in CCM is shown in Figure 4. Here, transition guards need to be selected such that fixed frequency PWM control scheme is implemented.

Fig. 4 Approximated waveforms of state variables

in DCM

The ripple inductor current is calculated from average output voltage at steady state and the change in  $i_L$  during  $\Delta t = D_1 T$  time as follows.

$$\Delta i_L = \frac{V_{in}(V_o - V_{in})}{2LfV_o} \tag{3}$$

The average inductor current -  $I_L$  can be derived by equating input and output power as below:

$$I_L = \frac{V_o^2}{RV_{in}} \tag{4}$$

From Figure 4, peak inductor current during CCM operation can be given as

$$I_{pk1} = I_L + \Delta i_L \tag{5}$$

From (8), peak current of the inductor depends on line and load conditions and it is considered as  $TG_{12}$ :  $i_L \ge I_{pkl}$  to control transition from mode- $k_l$  to mode- $k_l$ . The transition from mode- $k_l$  to mode- $k_l$  is determined by  $TG_{21}$ :  $t \ge T$ , where T is the time period.

# Supervisor (CCM/DCM detector)

Here, the supervisor must be designed to distinguish the CCM and DCM operations. While the inductor current is invariably greater than zero in CCM operation, it becomes zero for a short period of time in DCM operation. The latter condition occurs when the ripple current of inductor is higher than average inductor current. Thus, different operating modes are summarized as;  $I_L > \Delta i_L \Rightarrow$  CCM operation,  $I_L < \Delta i_L \Rightarrow$  DCM operation and  $I_L = \Delta i_L \Rightarrow$  CrCM operation.

# PFM Controller Design for DCM Operation

At light load condition, the inductor drains its total energy before the completion of switching cycle is called DCM operation. Figure 5 shows approximated inductor current and output voltage waveforms for DCM operation.

By using volt-sec balance and the average load current during  $D_2$  T time, we get the quadratic equation as below:

$$V_o^2 - V_o V_{in} - \frac{V_{in}^2 D_1^2 R}{2Lf} = 0 ag{6}$$

By rearranging the feasible solution of quadratic equation (6) and from Figure 5, the peak current of inductor for DCM operation is calculated as follows:

$$I_{pk2} = \sqrt{\frac{2V_o(V_o - V_{in})}{RLf}} \tag{7}$$

Thus, the peak current as per (7) determine the transition from mode-k1 to mode-k2. The transition from mode-k2 to mode-k3 is natural, and output voltage swing is considered for transition from mode- $k_3$  to mode- $k_1$ . Thus, the transition guards for DCM operation are TG<sub>12</sub>:  $i_L \ge I_{pk2}$ ,  $TG_{23}$ :  $i_L = 0$  and TG<sub>31</sub>:  $v_o = V_o$ .

$$f = \frac{V_o - V_{in}}{2\Delta v_o RC} \tag{8}$$

## 6.1.3 Simulation results and discussion for boost converter

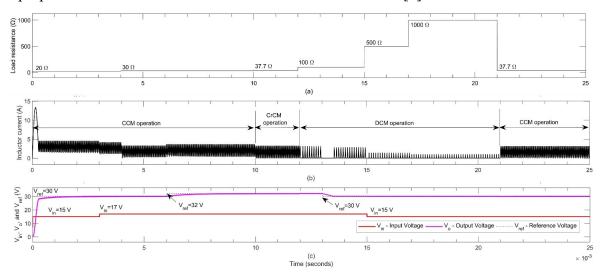

The simulation of proposed hybrid control scheme is implemented in MATLAB. The nominal parameters are  $V_{in} = 15$  V,  $L = 100 \mu$ H,  $C = 80 \mu$ F,  $R = 20 \Omega$ , and  $V_o = 30$  V. The potency of the suggested control scheme is given by substantial amount of line and load variations as shown in Figure 6. Table-4 shows duty cycle (*D*), percentage of peak overshoot (% $M_p$ ), and settling time ( $T_s$ ) during different line, load and set-point changes. The comparison of proposed scheme with PID and FOPID is shown in Table-5 [4].

**Fig. 6** Simulation results: variations in (a) load resistance, (b) inductor current, (c) input voltage (red), reference voltage (blue) and output voltage (pink)

|     | , r,      | ~          | C        |           | •           |       |       |

|-----|-----------|------------|----------|-----------|-------------|-------|-------|

| Sr. | Time span | R          | $V_{in}$ | $V_{ref}$ | D           | $M_p$ | $T_s$ |

| No. | (ms)      | $(\Omega)$ | (V)      | (V)       | (%)         | (%)   | (ms)  |

| 1   | [0-3)     | 20         | 15       | 30        | [0-46.4)    | 0     | 2.5   |

| 2   | [3-4)     | 20         | 17       | 30        | [46.4-44.5) | 0     | 0     |

| 3   | [4-6)     | 30         | 17       | 30        | [44.5-43.8) | 0.6   | 0.1   |

| 4   | [6-10)    | 30         | 17       | 32        | [43.8-46.9) | 0     | 3.5   |

| 5   | [10-12)   | 37.7       | 17       | 32        | [46.9-47.1) | 0.4   | 0     |

| 6   | [12-13)   | 100        | 17       | 32        | [47.1-28.8) | 1     | 0     |

| 7   | [13-15)   | 100        | 17       | 30        | [28.8-16.8) | 0     | 0.6   |

| 8   | [15-17)   | 500        | 15       | 30        | [16.8-9.7)  | 0     | 0     |

| 9   | [17-21)   | 1000       | 15       | 30        | [9.7-6.5)   | 0     | 0     |

| 10  | [21-25)   | 37.7       | 15       | 30        | [6.5-4.9)   | 0.6   | 1     |

**Table 4** D,  $M_p$ , and  $T_s$  during line, load and set-point variations

**Table 5** The performance comparison of proposed control scheme with PID and FOPID for boost converter

| Parameter              | PID     | FOPID   | Proposed Method      |  |

|------------------------|---------|---------|----------------------|--|

| $V_{o}\left( V\right)$ | 11.61   | 11.99   | 12                   |  |

| Rise time $(\mu S)$    | 432.533 | 606.711 | 269.770              |  |

| Slew rate $(mV/ms)$    | 21.839  | 15.805  | <b>26.362</b> (V/ms) |  |

| $\Delta Vo(V)$         | 0.5     | 0.001   | 0.125                |  |

| %M <sub>p</sub> (%)    | 27.564  | 1.531   | 0                    |  |

| Undershoot (%)         | -1.047  | 1.032   | 0                    |  |

| $T_s$ (ms)             | 19.919  | 0.432   | 3                    |  |

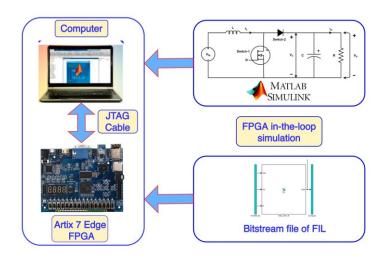

# 6.1.4 FPGA in Loop (FIL) implementation

In the realm of control algorithm validation and testing, the FIL technique emerges as a powerful solution [16, 17]. By integrating simulation software with field-programmable gate arrays (FPGAs), FIL enables the real-time verification of controllers within a simulation environment. To utilize FIL effectively, certain software and toolkit requirements must be met. These include using MATLAB for control algorithm development, along with FPGA design suite software such as VIVADO by XILINX or Quartus by Intel. Additionally, toolkits like HDL Coder, HDL Verifier, and DSP HDL Toolbox are essential components for successful implementation of the FIL technique.

Fig. 7 Block diagram of FIL validation for the proposed control algorithm

The FIL environment of MATLAB along with Xilinx vivado is used to implement control algorithms on ARTIX7 (XC7A35T) EDGE BOARD. The FIL block is generated using an HDL coder to load the filter algorithm on a selected FPGA device. Figure 7 provides a visual representation of the block diagram, demonstrating how the FIL technique is utilized to validate the proposed control algorithm.

# 6.1.5 Stability analysis

In this, the stability analysis of the control of SDS is focused on. Specifically, the local stability of the limit cycle within the system is examined. To establish the local stability, the Poincare map is employed, which is a powerful tool enabling the characterization of the system's behaviour at discrete intervals [18]. Additionally, to ensure convergence, the utilization of multiple Lyapunov functions is incorporated [19]. These Lyapunov functions play a crucial role in the assessment of the system's stability by providing valuable insights into the energy variations and stability properties.

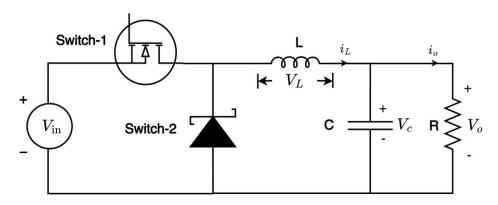

## 6.2 Buck Converter

In a standard circuit configuration of the buck converter, depicted in Figure 8, ideal components are initially assumed for analysis purposes. However, to ensure precise calculations and modelling, the compensation mechanism takes into account the influence of parasitic values. The design employs a boundary-based PWM control scheme tailored for CCM operation of the buck converter. Additionally, the analysis includes the evaluation of model mismatch, encompassing parametric variations and parasitic parameters. A comparison is also conducted between the proposed scheme and the PID and FOPID control schemes as shown in Table-6 [4].

Fig. 8 The circuit diagram of a conventional buck converter

**Table 6** The performance comparison of proposed control scheme with PID and FOPID for buck converter

| Parameter              | PID FOPID |         | Proposed Method |  |

|------------------------|-----------|---------|-----------------|--|

| $V_{o}\left( V\right)$ | 9.933     | 9.99    | 10              |  |

| Rise time (µS)         | 92.687    | 40.614  | 2.943           |  |

| Slew rate $(mV/ms)$    | 85.735    | 105.223 | 3863            |  |

| $\Delta Vo(V)$         | 0.02      | 0       | 0.006           |  |

| %M <sub>p</sub> (%)    | 15.698    | 0.505   | 0.503           |  |

| Undershoot (%)         | 2         | 2.066   | 1.997           |  |

| $T_s$ (ms)             | 19.98     | 0.003   | 3.535           |  |

# 7. Achievements with respect to objectives

The followings are the achievements resulting from the objectives mentioned above.

- A comprehensive mathematical model has been devised for the boost and buck converter, which incorporates mode-dependent parameters, leading to a significantly enhanced and precise representation of the system's dynamic behaviour.

- A specialized control algorithm was introduced for boost and buck converters, designed to proficiently manage mode transitions while ensuring stability, convergence, and desired performance during switching operations.

- By employing a rigorous stability analysis through the Lyapunov method and Jacobian Poincare map, the boost and buck converter's stability properties were thoroughly examined, resulting in successful establishment and valuable insights into the system's stability behaviour.

- Implemented the developed control algorithm on an Artix-7 FPGA board through the FIL technique, enabling real-time evaluation of the control system's performance in a hardware environment, validating its effectiveness and practical applicability. The implementation of the hardware on the Artix 7 Edge board using FIL enhances design flexibility, allowing for easy modifications and adaptations to the system.

- The proposed control algorithm for boost and buck converters was thoroughly compared with conventional methods, such as PID and FOPID, demonstrating its superiority in terms of dynamic characteristics, thereby contributing to advancements in control theory.

- Explored potential challenges and future directions for the refinement and application

of the proposed control strategy in practical systems, providing valuable insights for

future research and real-world implementation.

## 8. Conclusion

In this research, the focus lies on tackling the intricacies and obstacles associated with controlling dynamic systems that undergo mode transitions, specifically in the context of boost and buck converters. A comprehensive mathematical model is developed, taking into account mode-dependent parameters, thereby presenting a more accurate portrayal of system dynamics. The proposed control algorithm demonstrates remarkable robustness in managing mode transitions, ensuring stability, convergence, and desired performance during switching operations. To validate the system's stability properties, rigorous stability analysis is conducted using Lyapunov methods and Jacobian Poincare map. The practical applicability of the control

system is confirmed through successful FIL implementation on the Artix 7 Edge board, which also enhances design flexibility. Comparative performance evaluations clearly indicate the superiority of the proposed control algorithm over conventional methods. Furthermore, potential challenges and future directions are discussed in the synopsis, providing valuable insights for further refinement and real-world application of the control strategy. In summary, this research represents a significant advancement in understanding and effectiveness of control strategies for SDSs, offering valuable knowledge applicable to diverse domains with complex dynamic systems, particularly in the domain of boost and buck converters.

## 9. List of Publications

- H. Patel and A. Shah, "Boundary-Based Hybrid Control Algorithm for Switched Boost Converter Operating in CCM and DCM", *International Journal of Electrical and Electronics Research*, vol. 11, no. 1, pp. 213-221, March 2023. DOI: <a href="https://doi.org/10.37391/ijeer.110129">https://doi.org/10.37391/ijeer.110129</a> (Scopus Indexed)

- H. Patel and A. Shah, "Boundary-Based PWM Control Scheme for a DC-DC Buck Converter Operating in CCM", Transactions on Energy Systems and Engineering Applications, vol. 4, no. 1, pp. 1–17, Apr. 2023. DOI: <a href="https://doi.org/10.32397/tesea.vol4.n1.504">https://doi.org/10.32397/tesea.vol4.n1.504</a> (Scopus Indexed)

## 10. References

- [1] R. Madhana and G. Mani, "Power enhancement methods of renewable energy resources using multiport DC-DC converter: A technical review," *Sustainable Computing: Informatics and Systems*, vol. 35, p. 100689, 2022.

- [2] A. S. Samosir, T. Sutikno, and L. Mardiyah, "Simple formula for designing the PID controller of a DC-DC buck converter," *International Journal of Power Electronics and Drive Systems*, vol. 14, no. 1, p. 327, 2023.

- [3] L. F. d. S. C. Pereira, E. Batista, M. A. G. de Brito, and R. B. Godoy, "A Robustness Analysis of a Fuzzy Fractional Order PID Controller Based on Genetic Algorithm for a DC-DC Boost Converter," *Electronics*, vol. 11, no. 12, p. 1894, 2022...

- [4] K. Aseem and K. S. Selva, "Closed loop control of DC-DC converters using PID and FOPID controllers," *International Journal of Power Electronics and Drive Systems*, vol. 11, no. 3, p. 1323, 2020.

- [5] T. Kobaku, R. Jeyasenthil, S. Sahoo, and T. Dragicevic, "Experimental Verification of Robust PID Controller Under Feedforward Framework for a Nonminimum Phase DC–

- DC Boost Converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 3, pp. 3373-3383, 2021.

- [6] S. Ahmad and A. Ali, "Active disturbance rejection control of DC–DC boost converter: a review with modifications for improved performance," *IET Power Electronics*, vol. 12, no. 8, pp. 2095-2107, 2019.

- [7] J. Li and A. Wu, "Digital PWM-based boundary control for boost converter with exact feedback linearisation modelling," *International Journal of Electronics*, vol. 108, no. 2, pp. 180-200, 2021.

- [8] M. Z. bin Mohammad Suhaimi, A. A. Abd Samat, S. D. Nor, N. A. Othman, I. Hamzah, and M. Abdullah, "Design and implementation of digital controller for DC-DC boost converter," *International Journal of Advanced Technology and Engineering Exploration*, vol. 8, no. 74, p. 12, 2021.

- [9] L. Corradini, A. Babazadeh, A. Bjeletić, and D. Maksimović, "Current-Limited Time-Optimal Response in Digitally Controlled DC–DC Converters," *IEEE Transactions on Power Electronics*, vol. 25, no. 11, pp. 2869-2880, 2010.

- [10] J. Li and A. Wu, "Influence of Non-Ideal Factors on the Boundary Control of Buck Converters With Curved Switching Surfaces," *IEEE Access*, vol. 7, pp. 52790-52803, 2019.

- [11] M. Mirzaei and A. A. Afzalian, "Hybrid modelling and control of a synchronous DC-DC converter," *International Journal of Power Electronics*, vol. 1, no. 4, pp. 414-433, 2009.

- [12] G. Zhang, P. Zheng, S. Yu, H. Trinh, and P. Shi, "Controllability Analysis and Verification for High-Order DC–DC Converters Using Switched Linear Systems Theory," *IEEE Transactions on Power Electronics*, vol. 36, no. 8, pp. 9678-9688, 2021.

- [13] J. Lu, Z. She, W. Feng, and S. S. Ge, "Stabilizability of Time-Varying Switched Systems Based on Piecewise Continuous Scalar Functions," *IEEE Transactions on Automatic Control*, vol. 64, no. 6, pp. 2637-2644, 2019.

- [14] Z. Sun and S. S. Ge, *Stability theory of switched dynamical systems* (Communications and Control Engineering). Springer London, 2011.

- [15] A. Schaft and H. Schumacher, *An introduction to hybrid dynamical systems* (Lecture Notes in Control and Information Sciences). Springer London, 2013.

- [16] A. Gundogdu, R. Celikel, B. Dandil, and F. Ata, "FPGA in-the-loop implementation of direct torque control for induction motor," *Automatika*, vol. 62, no. 2, pp. 275-283, 2021.

- [17] V. K. Singh and R. N. Tripathi, "An FPGA Hardware-in-the-Loop Approach for Comprehensive Analysis and Development of Grid-Connected VSI System," *Energies*, vol. 16, no. 2, p. 759, 2023.

- [18] J. M. M. S. Gonçalves, "Constructive global analysis of hybrid systems," Massachusetts Institute of Technology, 2000.

- [19] P. Gupta and A. Patra, "A stable energy-based control strategy for DC-DC boost converter circuits," in 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No. 04CH37551), 2004, vol. 5: IEEE, pp. 3642-3646.